21日下午,来自新加坡国立大学的何丙胜副教授为我们带来了《Big Data onFurther Haradware》系列报告的第三场。此次报告主要介绍了如何基于GPU-CPU的异构架构构建新的数据系统以及新硬件未来的发展趋势和挑战。

报告伊始,何教授便为大家介绍了在新硬件的背景下做学术研究的方法。何教授指出,我们需要站在不同的角度去分析新硬件的发展带来的改变。从“一公尺”的角度来看,我们需要考虑如何让GPU和CPU发挥各自的优势,让两者更好的协作来提供更高处理性能;从“一公里”的角度来看,我们需要考虑如何设计一套编程策略,让上层的程序设计人员更充分地利用新硬件带了的性能优势。

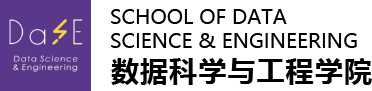

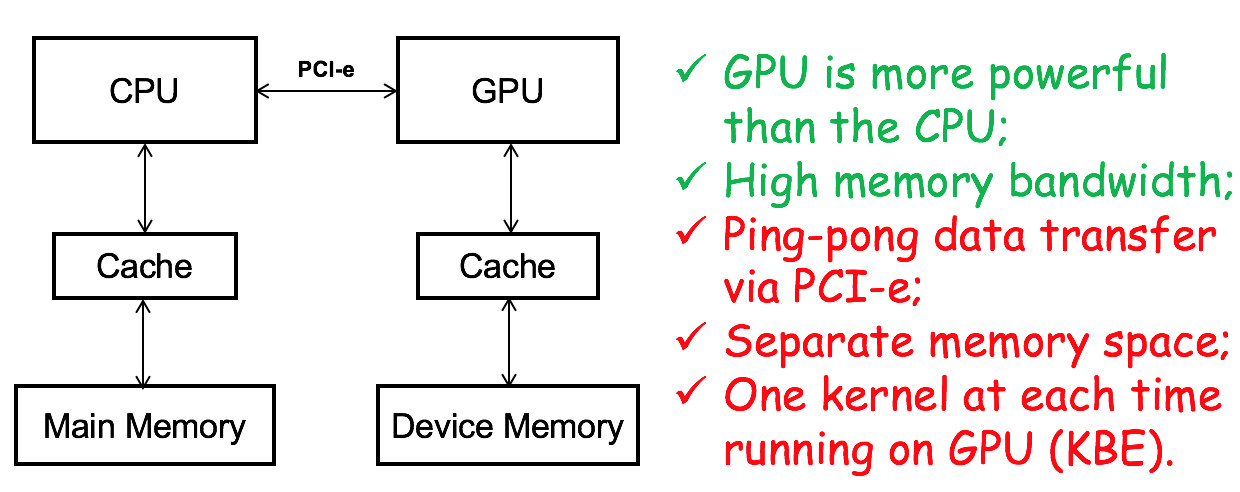

接下来,何教授介绍Discrete CPU-GPU Architectures(分离架构)和Coupled CPU-GPUArchitectures(协作架构)这两种新老GPU-CPU架构方式的优缺点。如下图1 所示,由于硬件之间的分离,GPU可以做到很高的处理核心数,从而提供远超于CPU的计算性能。同时,两者之间独立的架构又能保证各自拥有较高的内存带宽。然而,受限于分离的架构,GPU和CPU之间的通讯需要依赖于数据传输速率较低的PCI-e接口,这一限制就大大降低了CPU和GPU直接的数据传输效率。在这种分离架构下GPU和CPU都拥有各自独立的Cache和Memory,那么就需要额外的开销保证数据的一致性。相较于较早期的分离式架构,最新出现的相连架构去除了PCI-e互联方式,采用cache间通信方式消除了PCI-e通信带来的开销(如图2 所示)。这种架构方式使得上层系统可以将这两个处理器看作一个整体,从而更灵活的设计系统。但是,受限于芯片的大小,将CPU和GPU设计在一起后将降低GPU的处理核心数目,从而降低了GPU的性能。而当CPU和GPU共享一片Memory的时,Memory的带宽又成一个新的瓶颈。

图1 DiscreteCPU-GPU Architectures

图2 CoupledCPU-GPU Architectures

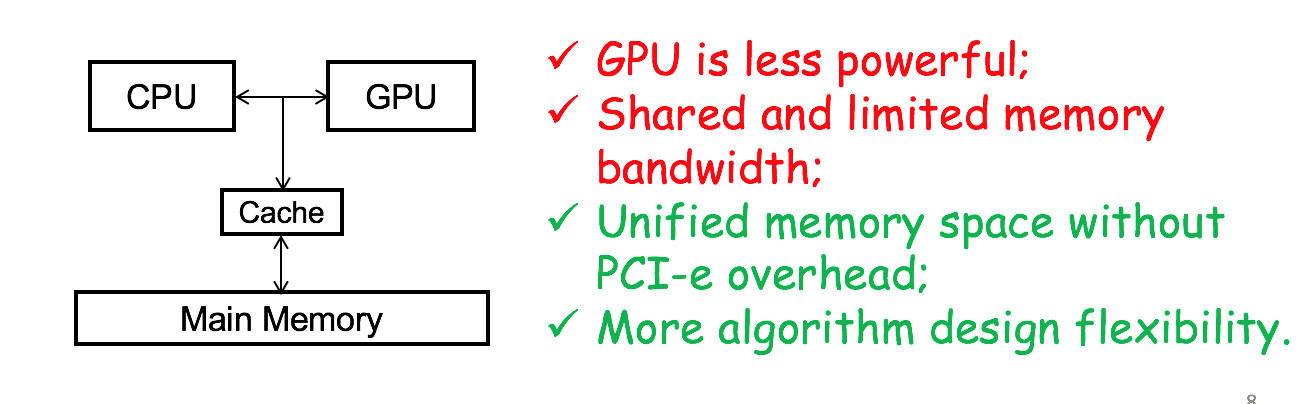

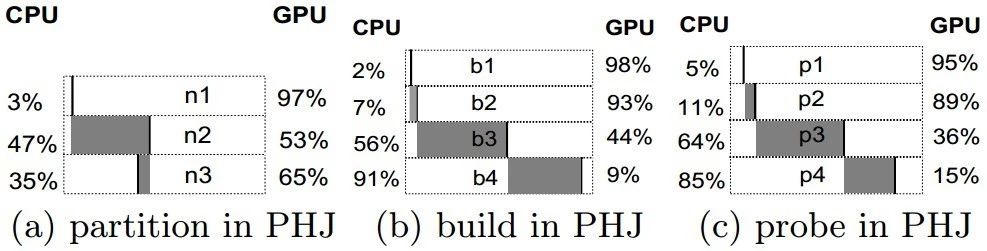

通过哈希连接(hash join)到查询处理(query process)再到查询处理优化(query process optimization)这“三步走”的策略,何教授团队分析GPU-CPU协作架构下的性能瓶颈,给出如何在新型CPU-GPU的架构下如何构建一个高性能的数据计算平台的策略。基于对hash join中操作特性的分析,何教授团队提出的Pipeline操作分配技术很好的解决了传统Off-Loading技术中的处理器等待问题和DATA-Dividing技术中操作分配到不合适的处理器的问题。从下图 3可见,无论是在simple hash join还是在partition hash join中pipeline操作分配技术的性能都明显优于Off-Loading技术和Data-Dividing技术。

图3 不同策略的时间开销对比

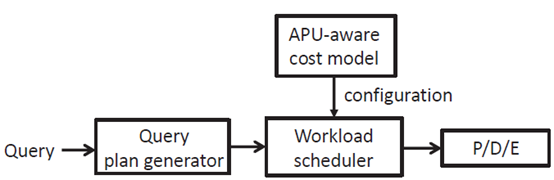

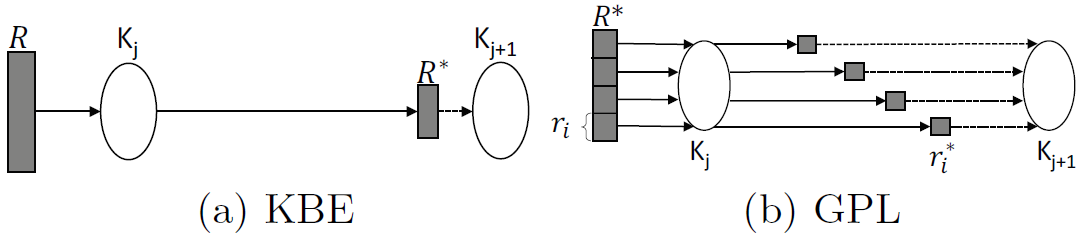

进一步分析hash join中各个阶段的执行,何教授团队发现memory stall开销在APU处理器(协作架构)上已经成为分离架构的两倍(如图4)。由于分离架构下处理器拥有更多的处理单元,这些多出来的处理单元便能够产生更多的并发线程去覆盖到memory stall的开销。因此,如何将降低memory stall便成为了在APU上做好查询处理的关键。如下图5所示,将查询分成预取(prefetch)、解压(decompression)和执行(execution)三个阶段,何教授团队便将问题转换成了在APU上调度这三个操作去覆盖memory stall。通过使用和hash join阶段类似的分配策略,memory stall的问题便可以得到很好地解决。

图4 hash join各阶段时间占用比

图5 查询处理架构

随着硬件设备的提升,GPU已经开始允许多核之间进行通讯。这个新技术的出现给APU上查询处理的优化带来了空间。如图6所示,由多核通讯带了的GPU并行处理技术很大程度上提升了GPU的资源利用率(resource utilization)来降低了stall的影响。

图6 GPU 并行pipeline技术

最后,何教授为大家列举了5点新硬件发展带来挑战:

(1) 软件的设计如何跟上硬件的发展?

(2)从原型(prototype)到工业产品(production)如何考量?

(3)传统系统的代码量巨大,如何维护支撑新硬件?

(4)系统的发展是通用化还是定制化?何去何从?

(5)商业化的硬件如何替代定制的硬件设备?

针对这几个挑战,何教授和大家分享了自己的看法和处理这些挑战的经验。

撰稿人:方祝和

排版:寿暖瑜