本次暑期学校邀请到新加坡国立大学的何丙胜教授给我们带来关于《Big Data Systems on Future Hardware》的3个系列报告。在20-21日期间,何教授将围绕“新硬件的发展给传统数据处理系统带来的挑战”、“设计充分利用硬件性能的数据结构与任务调度算法”、“构建GPU-CPU异构环境下的高性能查询处理系统”等3个关键问题介绍他所在团队的主要工作。

20日上午,DaSE2018暑期学校的同学们怀着求知的热情迎来了新加坡国立大学何丙胜教授的《Big Data Systems on Future Hardware》系列报告的第一场,何教授在报告一开始就明确指出“如何从一个小的数据结构开始分析新硬件带来的系统性能的变化”。

报告伊始,何教授便指出:“大数据的应用各种各样,存在很多挑战。譬如城市中的监控器以24帧每秒的速度产生图像数据,那么如何在这些持续增长的数据中找到某个人的行踪是一个难题。这些场景不仅仅需要优化算法,也更需要依赖硬件的革新。也就是说大数据的应用越来越需要考虑软硬件结合。” 接下来,何老师又通过一系列的案例来分享自己在利用新硬件来优化大数据应用的相关经验,并将其概括为如下面四个方面:

Why Hardware Matters?

Challenges & experiences in hardware-conscious research

Some example case studies

Future research directions

在这一次报告中重点介绍了1、2两个方面的内容。

1、Why Hardware Matters?

随着技术的发展,处理器的性能持续增加。尤其是一些新兴的协处理器(例如GPU)的处理性能越来越强于CPU。同时,内存和存储的价格也越来越便宜。也就是说硬件技术的发展降低获得相同性能的成本。那么就需要拥抱新硬件技术的发展。现在高性能兴新硬件不仅提供更高的并行度,同时也是多种多样。

处理器更加趋向于众核(many core)架构,支持更高的并行度,并且有多种加速器(协处理器)出现,像GPU、Xeon Phi,FPGA等。这些异构的处理器也趋向于紧密耦合,比如AMC APU是将CPU和GPU混为一体。除了计算性能,高带宽的内存也逐步出现,比如基于3D堆叠技术的3D-xpoint。这些新硬件在通用和专用不同方面努力。

在未来的硬件上,处理器可能有1000个核,并且有更多的异构和专用的硬件。软件的层次架构也更新。在未来的硬件层次中,“Disk is dead, NVRAM is disk, DRAM is cache, Locality is still the King”(磁盘已死,非易失内存是磁盘,内存是缓存,局部性依然至关重要)。同时随着网络技术的发展,集群会像私人电脑这样普遍。

兴新硬件提供高性能的计算、存储和网络,而另一方面大数据应用有多样化的需求。这两者之间存在如下三个方面的研究问题:

架构感知的优化:如何让当前的系统充分使用硬件的性能。这是一直以来的研究方向,存在于多个领域。

新硬件:如何根据应用的特点设计新的硬件,比如针对图形图形处理,设计出GPU。

新系统、应用:新的硬件催生新的系统,让以前的不可能成为可能,比如GPU加速AI的发展。

2、Challenges & experiences in hardware-conscious research

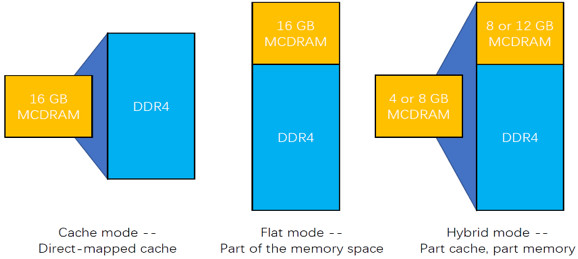

在数据库中,列存储的数据更易于压缩、并行、顺序访问,相比传统行存储的数据更适合于数据分析型的应用。另一方面,现有的主流CPU服务器基于NUMA架构,远端数据的访问代价远高于本地数据的访问,因此数据的局部性更加重要。但是由于带宽的限制,处理器中的核访问数据的代价很昂贵。而在众核处理器中(Intel Xeon PhiKnights Landing(KNL)),每个核访问片上的多通道内存(MCDRAM))的带宽达到400GB/s,但是访问内存数据受限于PCI-e上的带宽。如图 1 所示,MCDRAM与内存可以有以下三种放置方式。

图1 MCDRAM与传统内存的位置关系

Cache mode:把MCDRAM作为一个缓存级别,类似于传统的L3缓存。

Flat mode:将MCDRAM跟传统的内存放在同一个层次。

Hybridmode:将MCDRAM一部分作为cache,另一部分与内存水平放置。

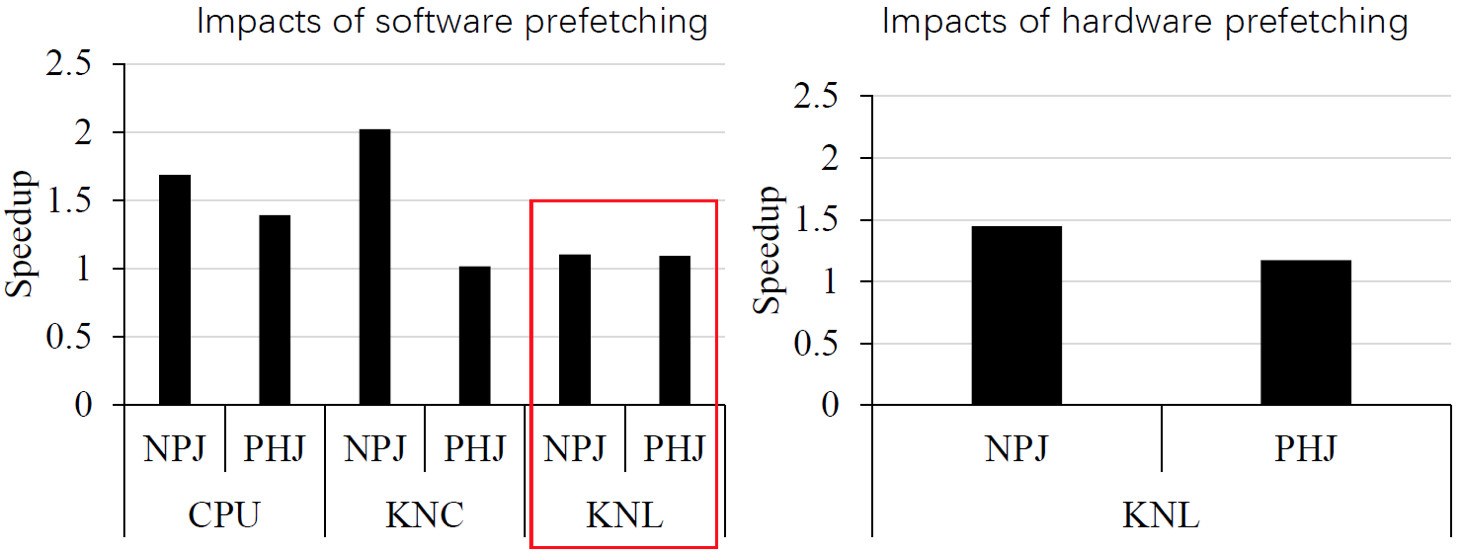

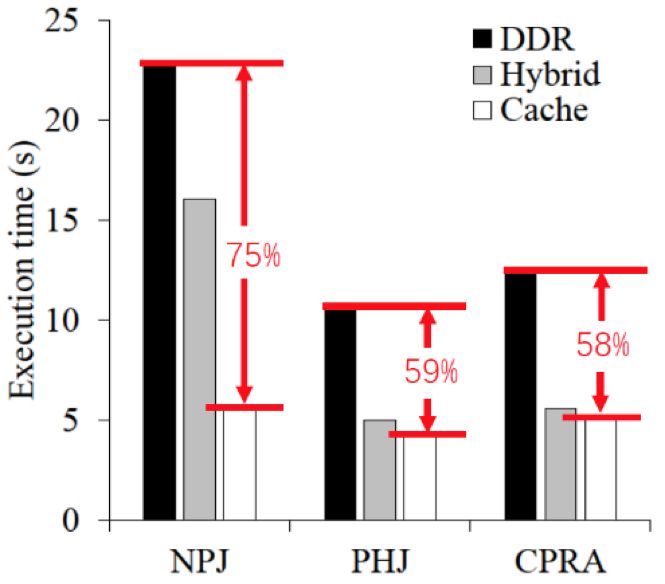

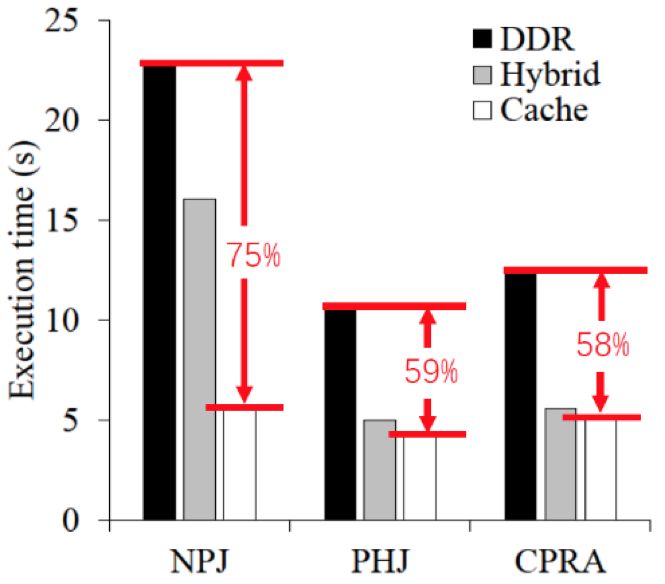

那么如何应用这样的众核处理器来加速数据库中广泛使用的哈希连接(hash join)?接下来何教授分享了他们一篇论文的成果,即《A Study of Main-Memory Hash Joins on Many-core Processor: A Case with Intel Knights Landing Architecture》。何教授指出,Hash join可以分为simple hash join(SHJ)和partitioned hash join(PHJ)。而影响这些算法性能有硬件参数也有软件参数,如何调整这些参数以达到hash join的最优性能是一个繁琐的工作。其中一种比较好的策略就是把这些参数降维,即找到参数之间的关系,着重控制重要的参数。经过探索发现,用户只需要控制线程数和MCDRAM的模式,根据硬件信息可以算出一些其他的参数。通过调整合适的参数,发现partitioned hash join的性能瓶颈在于随机访问内存。这一点可以进一步通过预取(prefetching)技术优化。如图2所示,在KNL上硬件预取比软件预取获得更大的提升。另外,针对传统的NUMA优化算法在KNL上面失效的问题,何教授他们提出的NUMA感知的join算法能够取得一定的优化,结果如图3所示。最后,最重要的是MCDRAM与内存的摆放模式对性能的影响,如图4所示,cache model能够取得75%的提升。由此可见,硬件感知的优化依然对hash join有重要影响。

图2 预取(prefetch)的作用

图3 NUMA感知的PHJ 图4 放置方式的影响

撰稿人:祝方和

排版:寿暖瑜